| Pré. | Proc. |

Statemachine Modélisation les HDL

Pour générer efficacement du code HDL (Hardware Description Language) à partir de modèles Statemachine , appliquez les pratiques de conception décrites dans cette rubrique. Les langages de description de matériel incluent VHDL, Verilog et SystemC.

Dans un modèle HDL Statemachine , vous pouvez vous attendre à :

- Désignez les déclencheurs de conduite

- Établir le mappage port-déclencheur

- Ajouter à la logique d' State Actif

Opérations

Opération |

La description |

Voir également |

|---|---|---|

|

Désignez les déclencheurs de conduite |

|

Statemachines Gâchette |

|

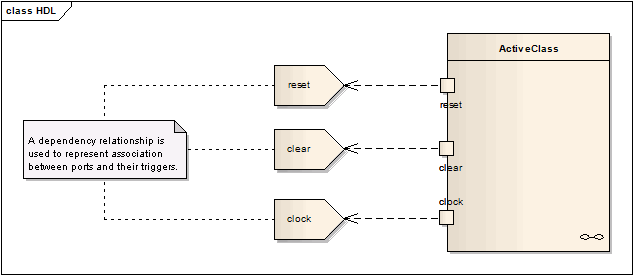

Établir le mappage port-déclencheur |

Après avoir modélisation avec succès les différents modes de fonctionnement du composant, et les Triggers qui leur sont associés, vous devez associer les Triggers aux Ports du composant. Une relation de dépendance entre le port et le déclencheur associé est utilisée pour signifier cette association. |

|

|

Actif State actif |

La désignation du Trigger pilote et l'établissement de la cartographie Port-Trigger mettent en place les préalables nécessaires à une interprétation efficace des composants matériels. Nous modélisons maintenant la logique réelle de Statemachine dans l' Actif (SubMachine) State . |

Notes

- Pour pouvoir générer du code à partir de modèles comportementaux, toutes les constructions comportementales doivent être contenues dans une classe

- Le moteur de génération de code actuel ne supporte qu'un seul déclencheur d'horloge pour un composant