| Pré. | Proc. |

Exemple Simulation électronique numérique

Pour cet exemple, nous parcourons la création d'un modèle SysPhS pour un circuit électronique numérique simple, puis utilisons une simulation pour prédire et cartographier le comportement de ce circuit.

Cet exemple fonctionne avec des composants qui ne sont pas inclus dans les composants communs SysPhS. Il exécute donc le processus de création de blocs pour correspondre aux composants externes à partir de zéro. Pour un webinaire illustrant cela, consultez le lien dans En savoir plus à la fin de la rubrique.

Prérequis

L'exécution de cette simulation nécessite :

- OpenModelica ou

- Simulink de MATLAB

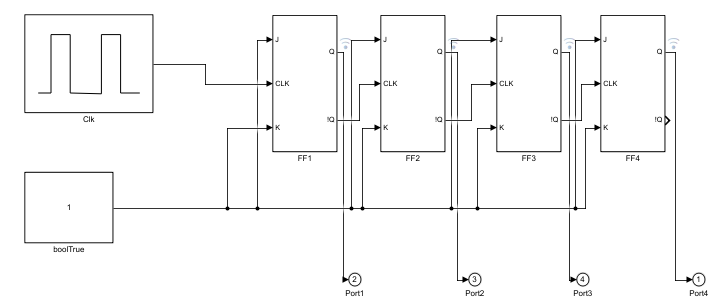

Diagramme de circuit - un diviseur de fréquence numérique

Le circuit électronique numérique que nous allons modéliser est représenté dans cette figure, qui utilise la notation standard des circuits électroniques.

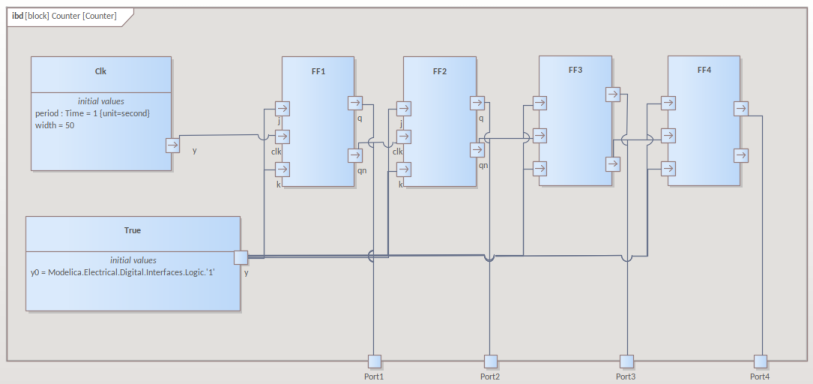

Le circuit de cet exemple comprend une source de signal numérique pulsé, quatre bascules et un état logique booléen vrai pour former un circuit diviseur de fréquence simple.

Créer Modèle SysML

Ce tableau montre comment nous pouvons créer un modèle SysML complet pour représenter le circuit, en commençant par les types de niveau le plus bas et en construisant le modèle une étape à la fois.

Composant |

Action |

|---|---|

|

Blocs |

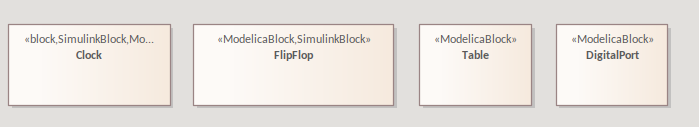

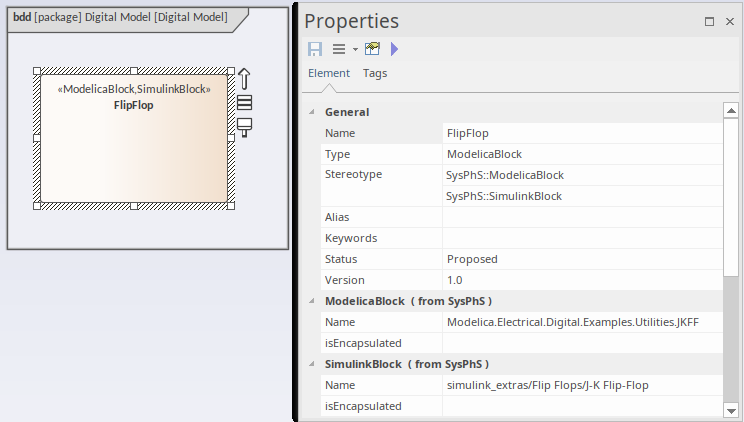

Dans SysML, en utilisant SysPhS, le circuit et chacun des types de composants peuvent être représentés à l'aide d'un Bloc . Créez d'abord un diagramme de définition Bloc (BDD) sous un Paquetage appelé ' Modèle numérique'. Dans le BDD, vous allez créer un ensemble de composants pour le circuit, sous forme de blocs SysML. Le circuit contient des représentations de quatre types de composants : une source de signal numérique pulsé, une bascule, un port booléen et un état logique booléen vrai. Ces composants sont de types différents, avec des comportements différents. Créez un Bloc SysPhS pour chacun des types de composants. Les composants de la définition Bloc interne (IBD) du circuit seront connectés via des ports, qui représentent pins électriques. Ceux-ci doivent être définis dans le BDD. Cette figure montre le BDD, avec des blocs définissant les types de composants utilisés. Note que ces blocs sont créés à partir de la boîte à outils SysPhS à l'aide de blocs Modelica ou de blocs Simulink. Vous pouvez saisir ces blocs dans les deux outils. Pour plus d'informations, consultez la rubrique d'aide Définition des blocs comme Modelica et Simulink . |

|

Définition du chemin Modelica et Simulink |

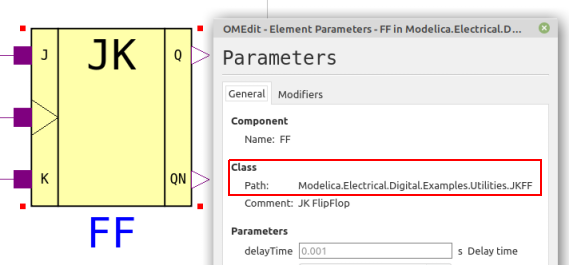

Afin de définir un Bloc spécifique à Modelica ou Simulink, vous devez accéder au Chemin du Composant dans l'application respective, puis le définir dans les Propriétés du Bloc . Par exemple, nous pouvons trouver le composant Flip-Flop dans Modelica. Nous copions ensuite cela dans les propriétés du Bloc . Pour plus de détails, consultez les rubriques d'aide Création de blocs spécifiques à Modelica et Création de blocs spécifiques à Simulink . |

|

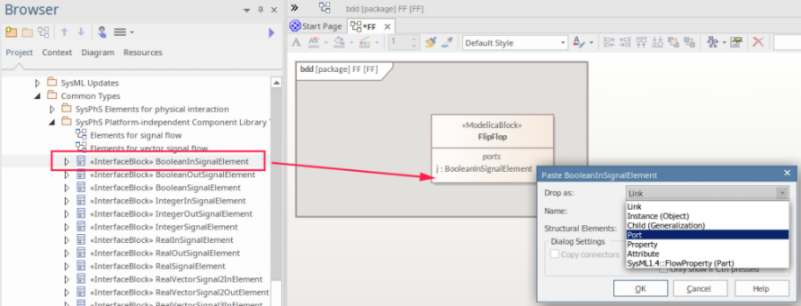

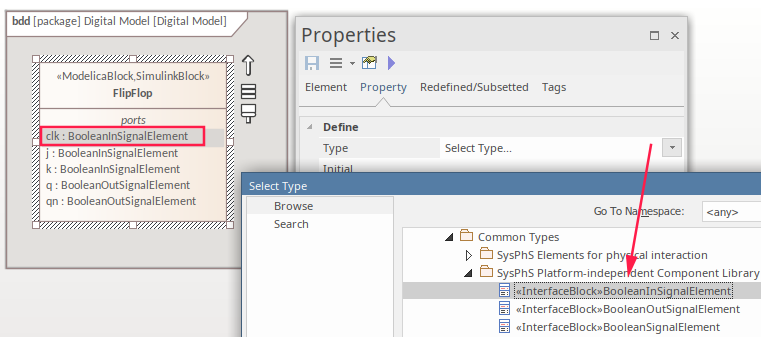

Ports PhS |

Pour définir les ports sur les blocs (dans ce cas, le port d'horloge Flip-Flop), faites glisser un port Modelica ou Simulink PhS sur le Bloc . Ce port doit ensuite être saisi sous la forme d'un BooleanInSignal. Note :

|

|

Types courants |

Pour commencer tous les modèles SysPhS, vous devez vous assurer que les types communs SysPhS sont chargés dans le référentiel et référencés dans le nouveau modèle, à l'aide du connecteur Paquetage Import. Pour plus d'informations, consultez Référencement des bibliothèques Simulation SysPhS Rubrique d'aide. Les types de valeur utilisés pour les ports sont prédéfinis dans les bibliothèques Simulation SysPhS. Les deux principaux types utilisés sont les types de valeur BooleanInSignal et BooleanOutSignal. Cette figure montre le Bloc Flip-Flop dans le diagramme de définition Bloc , avec le port d'horloge défini sur le type de valeur BooleanInSignal et celui-ci étant référencé dans la fenêtre Navigateur . |

|

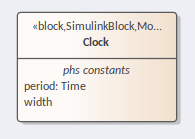

Constantes Phs |

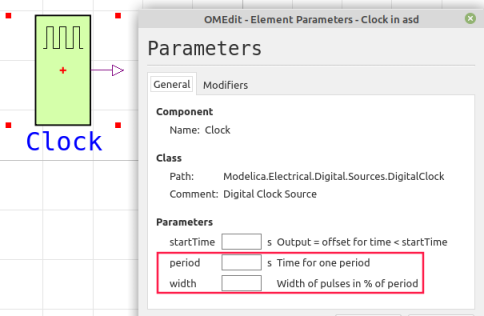

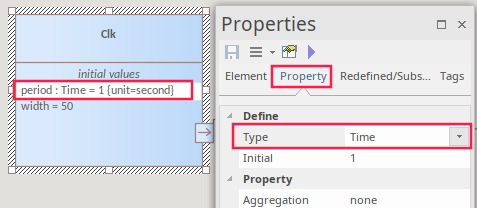

Les blocs Clock et Boolean-true ont tous deux des propriétés définies dans leurs composants respectifs dans MATLAB et Modelica. Prenons l'exemple de l'horloge. Pour ce type de composant, dans Simulink comme dans Modelica, nous devons définir une valeur pour la période de chaque impulsion et la largeur de chaque impulsion. Ces Propriétés doivent être définies et typées. La valeur des Propriétés sera définie dans l'IBD, le diagramme Paramétriques ou éventuellement dans les jeux de données de simulation. Pour définir la propriété définissant la période :

Pour définir les valeurs dans le composant individuel (Partie), consultez la ligne Valeurs initiales dans ce tableau . |

|

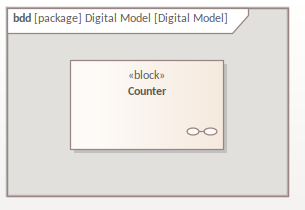

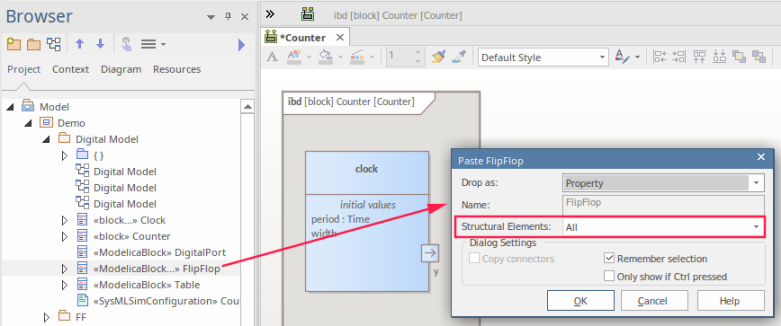

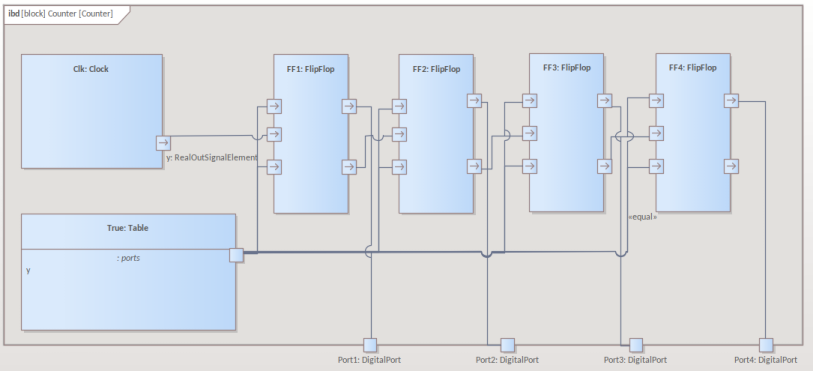

Structure interne - le circuit |

Pour la structure interne, nous créons un Bloc avec un diagramme IBD enfant.

|

|

Fixations |

Pour modéliser le câblage de ces composants :

Notez que cela suit la même structure que le diagramme de circuit d'origine, mais les symboles de chaque composant ont été remplacés par des propriétés typées par les blocs que nous avons définis. |

|

Valeurs initiales |

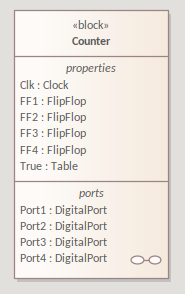

La source d'impulsions numériques est un composant DigitalClock dans Modelica et Simulink. Cela nécessite deux paramètres - « Période » et « Largeur », comme indiqué dans l'éditeur Modelica. Les valeurs de ces paramètres doivent être définies dans la partie IBD 'Clk', dans la fenêtre Propriétés , onglet 'Propriété', champ 'Initial' Les ports J et K nécessitent un état logique fixe « True ». Celui-ci est défini à l'aide d'un Tableau défini sur « true » à l'aide d'une valeur initiale, comme indiqué ici pour Modelica. En revenant au BDD, vous devriez maintenant avoir le Counter Bloc affiché comme suit : |

Configurer le comportement Simulation

Ce tableau montre les étapes détaillées de la configuration de SysMLSim.

Étape |

Action |

|---|---|

|

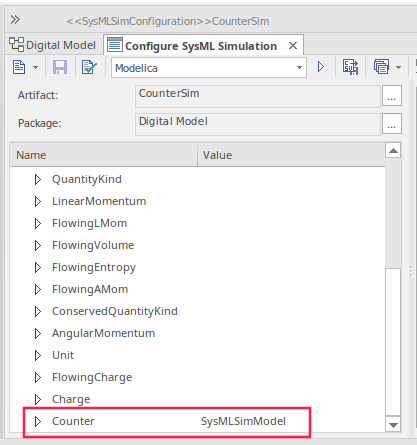

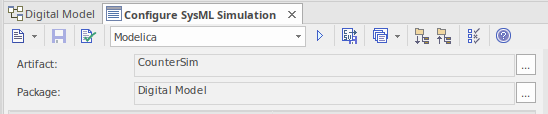

Créer un artefact SysMLSimConfiguration |

|

|

Définir le Paquetage |

|

|

Configurer Modelica ou Simulink |

Dans la liste déroulante supérieure, sélectionnez l’outil de simulation à utiliser :

|

|

Régler le Bloc pour simuler |

|

|

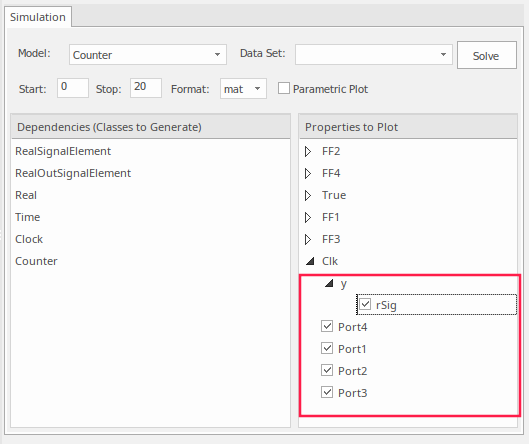

Sélectionner Propriétés à tracer |

Vous pouvez maintenant sélectionner les Propriétés à tracer :

|

Exécuter Simulation

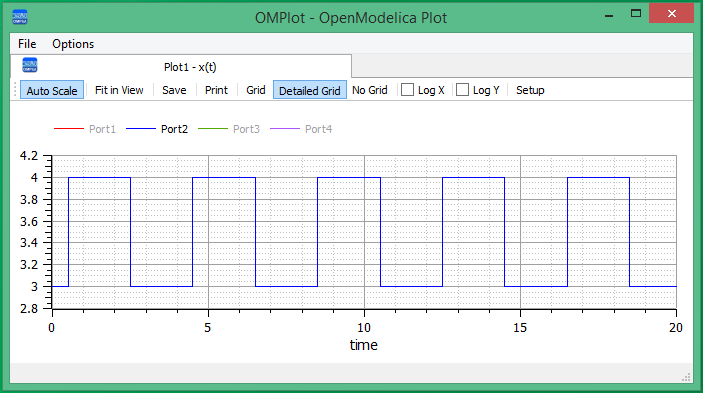

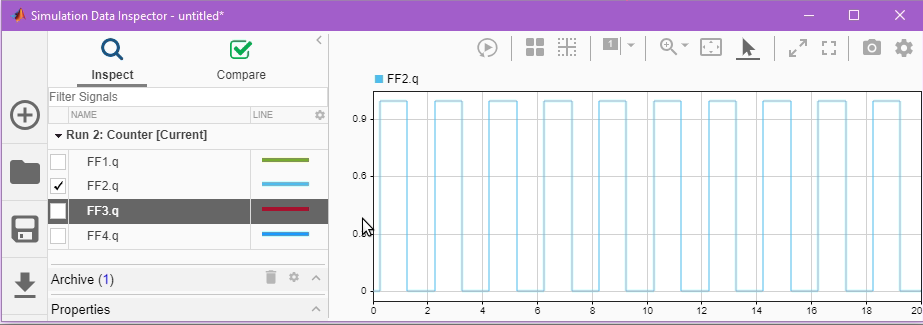

Sur la page « Simulation », cliquez sur le bouton Résoudre. Cela montre un exemple du tracé généré dans :

Modèleica

Simulink

Dans la légende, vous pouvez voir que le port 2 est sélectionné, tandis que les autres ports ont été désélectionnés pour afficher un tracé simple.

Vue le Modèle dans Modelica ou Simulink

Pour visualiser le modèle généré dans les applications externes, Modelica ou Simulink, consultez la rubrique d'aide Visualisation du Modèle généré . Consultez également les conseils de débogage des problèmes éventuels dans le code généré, dans la rubrique d'aide Conseils de débogage SysPhS .

Apprendre encore plus

- Référencement des bibliothèques Simulation SysPhS

- Utilisation des Motifs SysPhS

- Configurer Simulation SysML

- Affichage du Modèle généré

- Conseils de débogage SysPhS

- Création de blocs spécifiques à Modelica

- Créer des blocs spécifiques à Simulink et Simscape

- Configuration des blocs à la fois comme Modelica et Simulink

- Webinaire : SysPhS Digital example

- WebEA : Digital model Modelica

- WebEA : Digital model Simulink